CPU 架构

{Back to Index}

Table of Contents

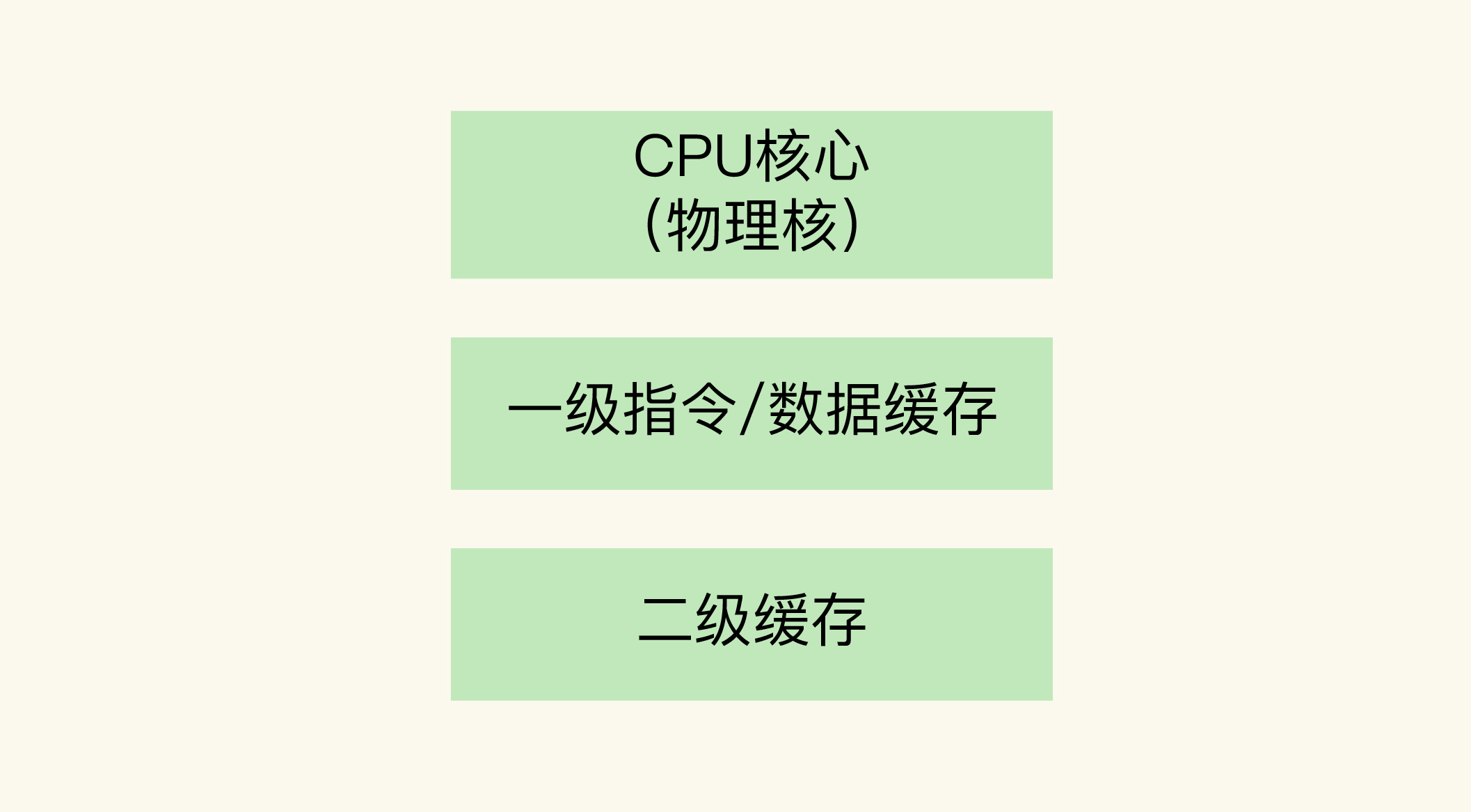

1 L1/L2 缓存

Figure 1: CPU 物理核架构

L1 和 L2 缓存是每个物理核 私有的 ,当数据或指令保存在 L1,L2 缓存时,物理核访问它们的延迟 不超过 10 纳秒 ,速度非常快。

2 L3 缓存

L1 和 L2 缓存的大小受限于处理器的制造技术,一般只有 KB 级别,存不下太多的数据。如果 L1、L2 缓存中没有所需的数据,应用程序就需要访问内存来获取数据。而应用程序的访存延迟一般在 百纳秒 级别,是访问 L1、L2 缓存的延迟的近 10 倍,不可避免地会对性能造成影响。

所以,不同的物理核还会 共享 一个共同的三级缓存。L3 缓存能够使用的存储资源比较多,所以一般比较大, 能达到几 MB 到几十 MB ,这就能让应用程序缓存更多的数据。当 L1、L2 缓存中没有数据缓存时,可以访问 L3,尽可能避免访问内存。

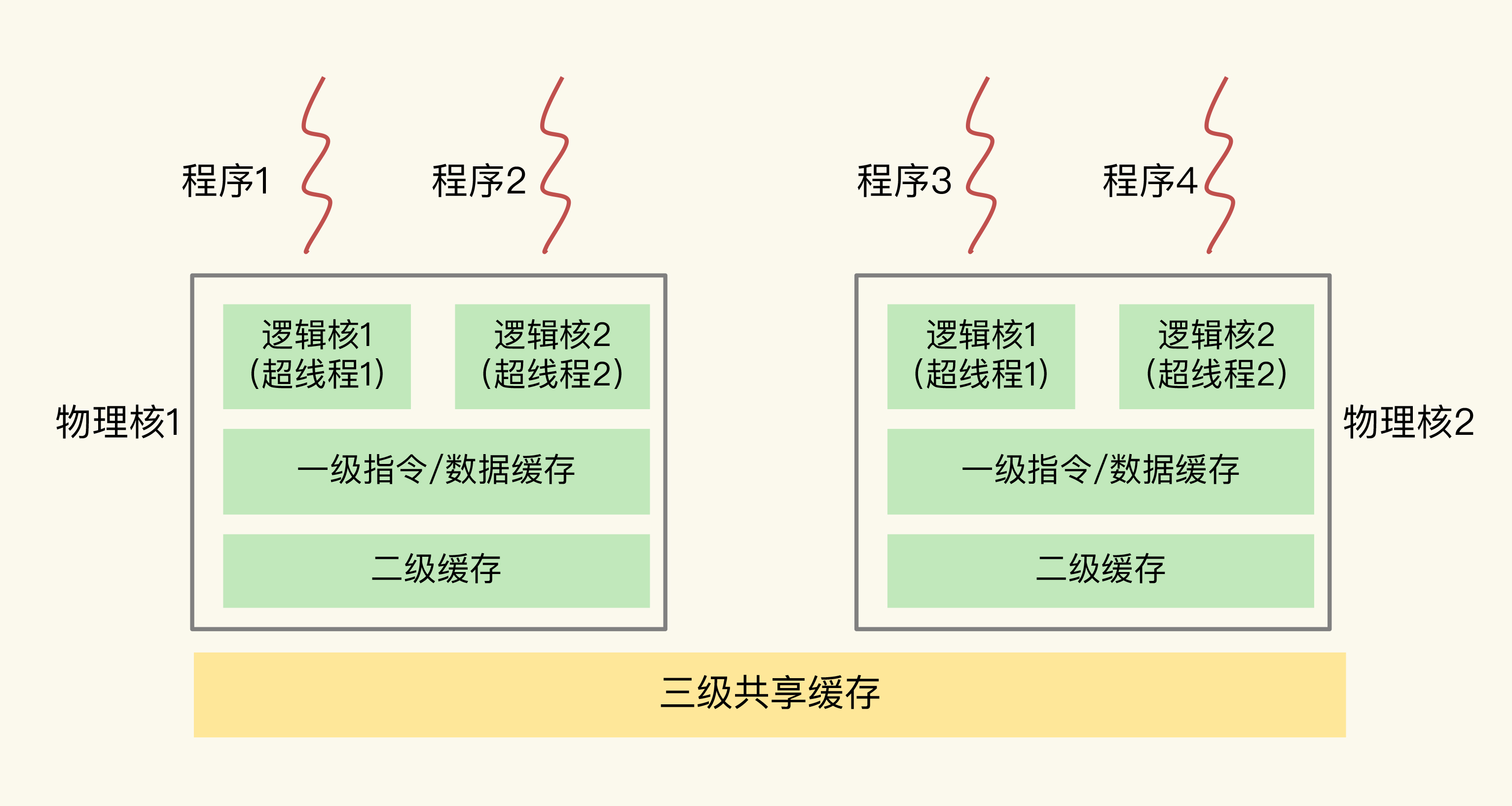

3 逻辑核

另外,主流的 CPU 处理器中,每个物理核通常都会运行两个 超线程 ,也叫作逻辑核。 同一个物理核的逻辑核会共享使用 L1、L2 缓存。

Figure 2: 物理核和逻辑核,以及一级、二级缓存的关系

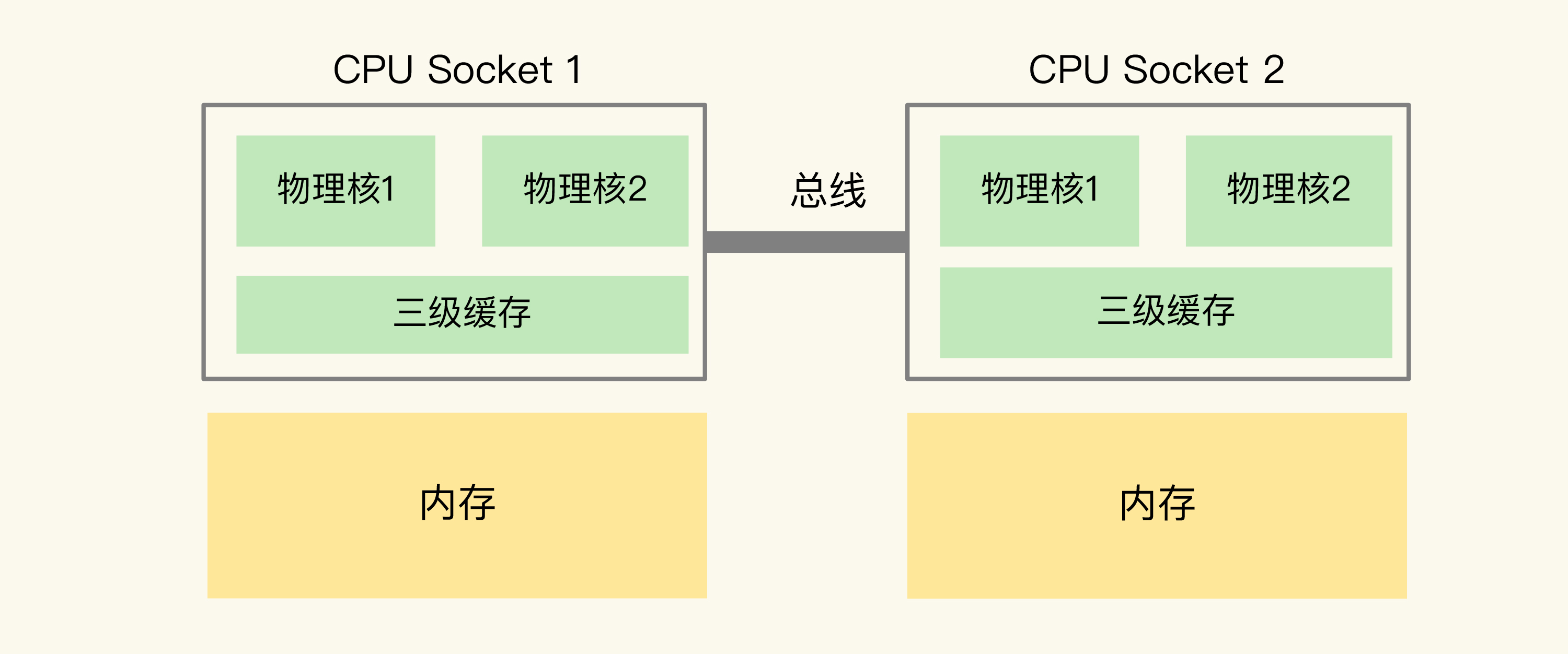

4 NUMA

CPU 处理器也称为 Socket ,在主流的服务器上,一个 Socket 会有 10 到 20 多个物理核。同时,为了提升服务器的处理能力, 服务器上通常会有多个 Socket,每个 Socket 有物理核(包括 L1、L2 缓存),L3 缓存,以及 连接的内存 ,同时,不同处理器间 通过总线连接 。

Figure 3: NUMA 架构

在多 CPU 架构上,应用程序可以在不同的处理器上运行。比如上图中应用程序可以先在 Socket 1 上运行一段时间,然后再被调度到 Socket 2 上运行。

如果应用程序先在一个 Socket 上运行,并且把数据保存到了内存,然后被调度到另一个 Socket 上运行,此时,应用程序再进行内存访问时,就需要访问之前 Socket 上连接的内存,这种访问属于 远端内存访问 。和访问 Socket 直接连接的内存相比, 远端内存访问会增加应用程序的延迟 。

在 NUMA 架构下,经常发生某一个节点内存不够,但其他节点内存充足的情况下,依旧使用到了 Swap ,进而导致软件性能急剧下降的例子。 这通常是因为 CPU Socket 对应的内存不够了,但它 可能不会去另一个节点申请内存 。(可以通过配置操作系统内存回收策略改变这种行为:本节点回收内存/其他节点申请内存/内存数据换到 Swap 的倾向程度)